우리가 FPGA를 사용하다 보면 디지털 I/O 입력으로 LVDS입력을 받거나, DDR방식으로 입력을 받아 처리를 해야 할때가 종종있다. 주로 고속 인터페이스 신호일 때 사용하는데 Xillinx 사의 VIVADO Tool 을 사용해서 개발할 때 한번 알아보도록 하자.

(이 내용은 기본적인 VIVADO 프로젝트를 만들어 사용할줄 아는 전제하에 시작하는 거니 잘모를때는 VIVADO 사용란에 있는 문서를 먼저 봐야한다.)

I/O 관련된 매뉴얼은 Xillinx 홈페이지에 가서 “ug471_7Series_SelectIO” 문서를 찾아보면 된다.

1) LVDS 입력을 위해서 하기 블록을 보자.

위 그림에서 보면 LVDS RX블럭의 “A” 블럭을 설정해주어야 이후에 나오는 “B” 블럭부터 기존에 Single Signal형태의 신호를 가지고 사용자가 코드를 구현할수 있다.

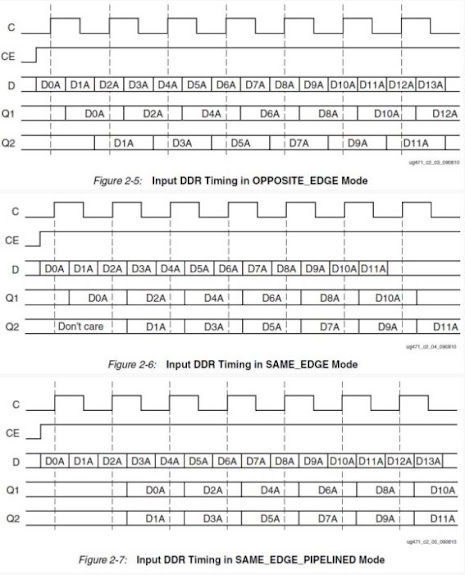

2) DDR 방식의 입력은 CLK의 High, Low 두개의 타이밍에 각각 다른 데이타가 들어오는 것을 말하는데 우리가 사용할때는 CLK의 Rising Timing에 2개의 데이타를 만들어서 사용하는작업을 해주어야 한다.

이제 위 설정들을 어떻게 해주어야 하는지 확인해보자.

프로젝트 설정이 완료된후 LVDS I/O 입력처리를 위해서 Templates를 이용해야 한다.

Library UNISIM;

use UNISIM.vcomponents.all;

위 2줄이 있어야 Templastes를 사용할수 있고, IBUFDS를 찾아서 사용하면 된다. Templastes는 Component와 같이 선언해주지 않고 바로 사용이 가능하다.

LVDS to Single은 아래와 같이 IBUFDS를 사용하면 되고, 사용자는 O에 연결된 Single Signal 사용이 가능하다.

u0 : IBUFDS port map ( O => lvds_clk, I => clk_p, IB => clk_n);

u1 : IBUFDS port map ( O => lvds_ch1, I => ch1_p, IB => ch1_n);

이제 LVDS로 들어온 (clk_p, clk_n) (ch1_p, ch1_n) 신호를 lvds_clk , lvds_ch1 처럼 한 개의 신호로 만들었다. 일반적인 신호는 이 상태에서 사용자가 코드 작성을 하면 된다.

만약 DDR방식으로 들어온 LVDS라고 하면 한단계를 더 거쳐야 한다.

IDDR을 Templates에서 찾아보자.

여기서 사용자가 선택해주어야 할 것은 DDR_CLK_EDGE이다.

총3개의 “OPPOSITE_EDGE” , “SAME_EDGE”, “SAME_EDGE_PIPELINED” 가있다.

이제 위와 같은 방식으로 LVDS, DDR방식의 신호를 사용할수 있다.